1. Tujuan [kembali]

- Memahami cara kerja Flip-Flop dan aplikasi dalam dunia elektronika

- Mengenal macam-macam Flip-Flop dari jenis Low dan High Input

2. Alat dan Bahan [kembali]

Flip-Flop, seperti yang disebutkan sebelumnya, adalah sirkuit bistable. Kedua status keluarannya stabil. Sirkuit tetap ada dalam kelauran tertentu tanpa batas sampai sesuatu dilakukan untuk mengubah status keluaran itu. Mengacu rangkaia multivibrator bistable yang dibahas sebelumnya, kedua status ini adalah transistor keluaran dalam saturasi (Output LOW) dan dalam cut-off (Ouput HIGH). Jika LOW dan kelauran HIGH masing-masing dianggap sebagai '0' dan '1', maka keluaran tersebut dapat berupa '0' atau '1'.

Karena baik '0' atau '1' dapatditahan tanpa batas waktu sampai sirkuit dipicu dengan tepat untuk pergi ke keadaan lain, sirkuit diaktan memiliki memori, ia mampu menuyimpan satu digit biner atau satu bit informasi digital.

Juga, jika kita mengingat fungsi rangkaian multivibrator bistable, kita temukan bahwa, ketiak salah satu transistor dalam keadaan jenuh, yang lainnya terputus. Ini menunjukkan bahwa jika kita keluaran yang diambil dari kolektor kedua transistor, maka kedua kelauran tersebut akan saling melengkapi. Dalam berbagai jenis Flip-Flop yang tersedia dalam bentuk IC, kita akan melihat bahwa semua perangkat ini menawarkan kelauran pelengkap yang biasanya disebut Q dan Q'.

Flip-FLop R-S adlah yang paling dasar dari semua Flip-Flop. Huruf R dan S disini adalah singaktan dari Reset dan Set. Ketika flip-flop Set, output Q-nya berubah menjadi status 1, dan ketika Reset ia berubah ke status 0. Keluaran Q merupakan pelengkap dari keluaran Q setiap saat.

R-S Flip-Flop terbagi menjadi:

- R-S Flip-Flop with Active Low Inputs

Pengoperasian Flip-Flop R-S pada gambar 10.17 dapat diringkas sebagai berikut:

- Set = Reset = 1 adalah kondisi istirahat normal dari flip-flop. Ini tidak berpengaruh pada status keluaran flip-flop. Baik keluaran Q dan Q tetap dalam keadaan logika sebelum kondisi masukan ini.

- Set = 0 dan Reset = 1 mengatur flip-flop. Q dan Q' masing-masing menuju ke status 1 dan 0

- Set = 1 dan Reset = 0 me-reset atau menghapus flip-flop. Q dan Q' menuju ke status 0 dan 1

- Set = Reset = 0 dilarang karena kondisi seperti itu mencoba untuk mengatur (yaitu Q = 1) dan mengatur ulang ( Q = 1) flip-flop pada saat yang sama. Untuk lebih tepatnya, input Set dan Reset di R-S flip flop tidak dapt aktif pada saat yang bersamaan.

- R-S Flip-Flop with Active High Inputs

Gambar 10.18 menunjukkan implementasi gerbang NAND lain dari flip-flop R-S. dan masing-masing menunjukkan simbol rangkaian dan tabel fungsinya. Sirkuit seperti itu akan memiliki input High Actif. Kombinasi input R = S = 1 akan dilarang sebagai input Set dan Reset dalam R-S flip-flop tidak dapat aktif pada saat yang bersamaan.

- Clocked R-S Flip-Flop

Dalam kasus flip-flop R-S clock atau dalam hal ini flip-flop clock, output berubah menyatakan sesuai input hanya pada terjadi pulsa clock. Flip-Flop clocked bisa menjadi level-triggered satu atau edge-triggered.

10.4 R-S Flip-Flop dengan Active Low Inputs

Dalam flip-flop yang dipicu level, output merespon data yang ada di input selama waktu tersebut tingkat pulsa High (atau Low). Artinya, setiap perubahan pada input selama jam aktif (High atau Low) direfleksikan pada output sesuai tabel fungsinya. Flip-Flop R-S clock dijelaskan di paragraf sebelumnya adalah flip-flop yang dipicu level yang aktif pada waktu High. Dalam flip-flop yang dipicu output merespon data pada input hanya pada Low-to-High atau transisi High-to-Low dari sinya clock. Flip-flop dalam dua kasus disebut sebagai positif edge dipicu dan edge negatif dipicu masing-masing.

Setia perubahan masukan selama ini pulsa clock High ( atau Low) tidak berpengaruh pada output. Dalam kasis Edge-triggered flio-flop, rangkaian detektor tepi mengubah input jam menjadi pulsa yang sangat sempit lebar beberapa nanodetik. Denyut nadi semput ini bertepatan dengan Low-to-High atau High-to-Low transisi waktu input. tergantung pada apakah itu flip-flop yang dipicu tepi positif atau flip-flop yang dipicu tepi negatif. Denyut ini sangat sempit sehingga pengoperasian flip-flop dapat dilakukan dianggap telah terjadi di tepi itu sendiri. Gambar 10.23 menunjukkan clock R-S flip flop dari gambar 10.21 dengan blok detektor tepi digabungkan di sirkuit jam. Gambar 10.24 masing-masing menunjukkan rangkaian detektor tepi tipikal untuk positif dan pemicu tepi negatif. Lebar pulsa sempit yang dihasilkan oleh rangkaian detektor tepi ini adalah sam dengan penundaan propagasi inverter.

4. Example [kembali]

Example : 10.4 halaman 389

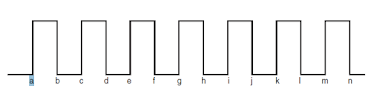

Bentuk gelombang persegi 100 KHz dari gambar 10.32 (a) diterapkan ke input jam dari yang ditunjukkan pada gambar dibawah ini.

Answer :

Tidak ada komentar:

Posting Komentar